btw, ima 2 externa trigera, 2 externa kloka.

interni trigeri su vrlo zanimljivi ... prvo se podesi "odnos" koliko podataka zelimo pre trigera a koliko posle, na primer ako stavino 20:80 i 10K semplova imacemo 200K semplova pre trigera i 800K semplova posle trigera

trigeri:

1. simple parallel trigger

u ovom modu se odabere "koji" pinovi nas zanimaju za trigger (moze bilo koja kombinacija postojeca 32 pina) i koje vrednosti tih pinova zelimo, kada se postigne to zeljeno stanje kresne se triger.

2. simple serial trigger

u ovom modu se odabere "niska" seriska za jedan kanal, kada se ta niska "desi" kresne se triger

3. komplex parallel trigger

setuje se kao za jednostavni paralelni ali ima 4 nivoa, za svaki nivo se bira da li trigger "prelazi na sledeci nivo" ili okida trigger

4. komplex serial

isto kao paralelni samo za serisku nisku, 4 nivoa, svaki nivo moze da bude na svom portu

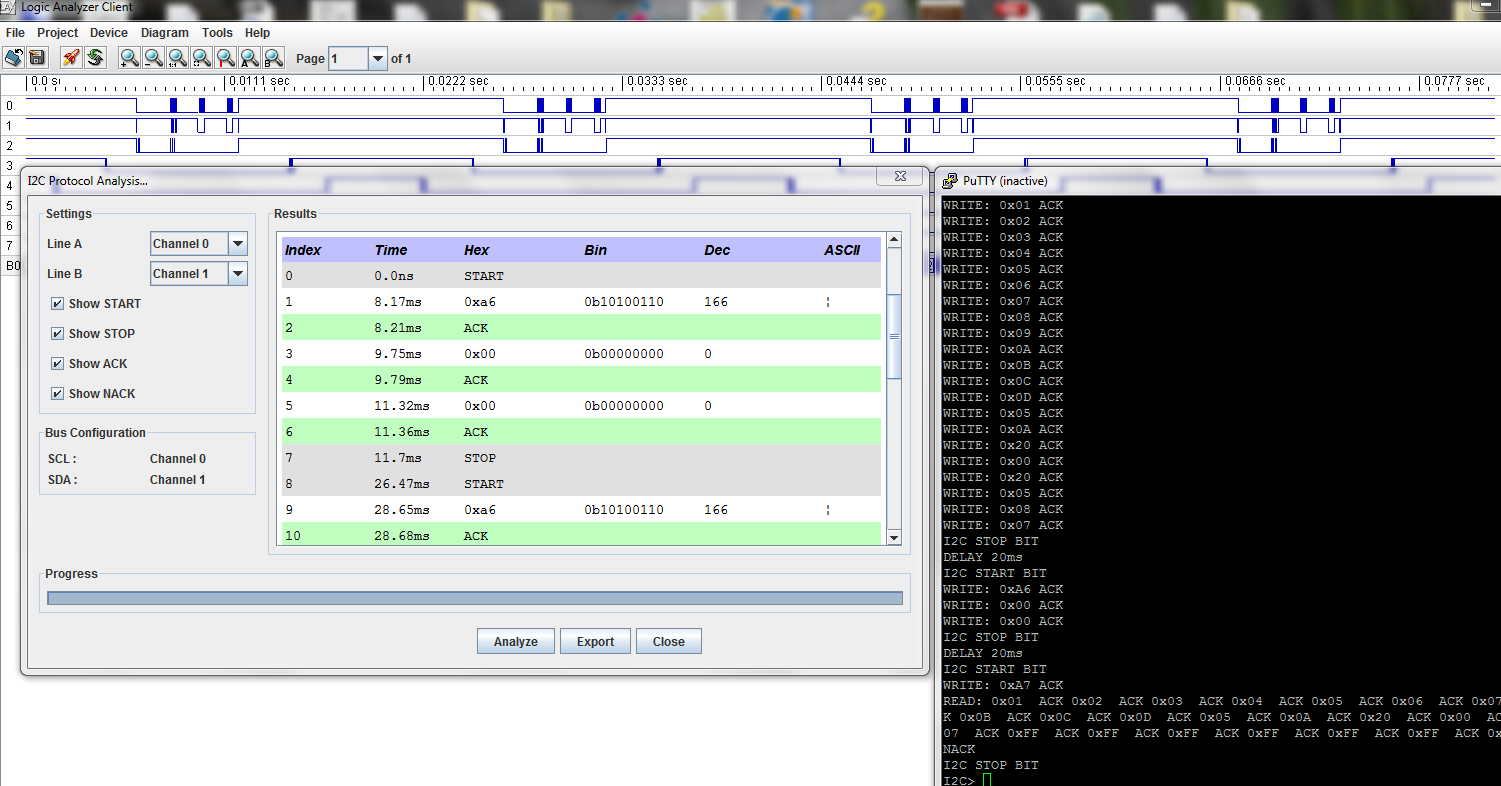

mnogo iskusna sprava .. java klijent nije nesto "ludo dobar" ali je pristojan i radi extra dekodiranje seriskog i i2c protokola, ostale jos nisam probao ali 400K i2c dekodira ko od sale. na zalost 24K koliko je meni sada podeseno je malo za neki duzi i2c stream ... doduse tu je vhdl :) pa ko ume .. dodatno, ovaj "unbuffered" port 16 bitni bidirekcioni je namenjen za extenzije, teoretski tu moze da se stavi dodatni SRAM sa malo vise memorije od toga sto ima interno, doduse 16 pinova mozda nije dovoljno...

ja sam inace pre nego sto je ovo stiglo krenuo da pravim slicnu spravu sa cpld + externi sram posto imam neku ideju odavno da to probam .. a imam i sram :) pa cu videti .. hteo sam da napravim sa ADC-om da imam 8 bitni logic analyzer + 8bitni ADC koje sinhrono skeniram, tu cpld sluzi generalno za triggering, inace bi mogao to sa obicnim brojacem i mcu-om, ali za trigere mi je jeftinije sa cpld-om (inace bi bilo mnooogo 74hc* na ploci) - generalno odlicna vezba za ucenje vhdl-a :)